# Product layout induced topography effects on intrafield levelling

J-G Simiz, T Hasan, F Staals, B Le-Gratiet, Wim T. Tel, C Prentice, A

Tishchenko

# ► To cite this version:

J-G Simiz, T Hasan, F Staals, B Le-Gratiet, Wim T. Tel, et al.. Product layout induced topography effects on intrafield levelling. EMLC 2015, 31st European Mask and Lithography Conference, Jun 2015, Eindhoven, Netherlands. pp.96610R, 10.1117/12.2194079. ujm-01272856

# HAL Id: ujm-01272856 https://ujm.hal.science/ujm-01272856

Submitted on 15 Feb 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Product layout induced topography effects on intrafield levelling

J-G. Simiz<sup>1,4</sup>, T. Hasan<sup>2</sup>, F. Staals<sup>2</sup>, B. Le-Gratiet<sup>1</sup>, W.T. Tel<sup>2</sup>, C. Prentice<sup>3</sup>, A. Tishchenko<sup>4</sup>

<sup>1</sup>STMicroelectronics, 850 rue Jean Monnet, F-38926 Crolles Cedex, France

<sup>2</sup>ASML, De Run 6501, 5504DR Veldhoven, the Netherlands

<sup>3</sup>ASML SARL, 459 chemin des Fontaines, F-38190 Bernin, France

<sup>4</sup>LaHC CNRS-UMR 5516, 18 Rue du Professeur Benoît Lauras, F-42000 Saint-Étienne, France

#### Abstract:

With continuing dimension shrinkage using the TWINSCAN NXT:1950i scanner on the 28nm node and beyond, the imaging depth of focus (DOF) becomes more critical. Focus budget breakdown studies [Ref 2, 5] show that even though the intrafield component stays the same, it becomes a larger relative percentage of the overall DOF. Process induced topography along with reduced Process Window can lead to yield limitations and defectivity issues on the wafer. In a previous paper, the feasibility of anticipating the scanner levelling measurements (Level Sensor, Agile and Topography) has been shown [1]. This model, built using a multiple variable analysis (PLS: Partial Least Square regression) and GDS densities at different layers showed prediction capabilities of the scanner topography readings up to 0.78 Q<sup>2</sup> (the equivalent of R<sup>2</sup> for expected prediction). Using this model, care areas can be defined as parts of the field that cannot be seen nor corrected by the scanner, which can lead to local DOF shrinkage and printing issues. This paper will investigate the link between the care areas and the intrafield focus that can be seen at the wafer level, using offline topography measurements as a reference. Some improvements made on the model are also presented.

#### **KEYWORDS:**

depth of focus, intrafield, scanner levelling, topography, GDS, product design layout effect, PLS regression analysis, optical lithography

# **INTRODUCTION**

For 193 nm immersion lithography focus control is limited by the topography measurement accuracy combined with the scanner correction capability. For the critical features on the layer investigated, the depth of focus is of the same order as the scanner correction capability. This is, in part, driven by high frequency topography effects that cannot be handled fully by the scanner's wafer levelling & focussing systems. Product layout induced topography is an important factor that combined with tight focus control and low DOF values can lead to local yield loss.

In this paper, topography correlation to on-product focus was investigated with the ultimate goal of linking GDS to topography and focus. A new way of using topography data and product layout knowledge is, also, presented by using this information to determine optimized weighting factors during scanner levelling. This work was done on the Contact layer on the 14FDSOI development shuttle.

# I – METHODOLOGY / CONCEPT

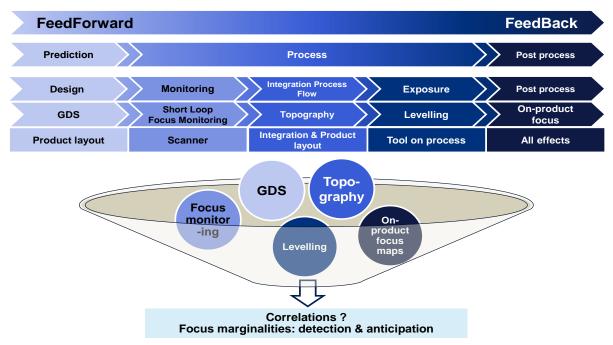

In a previous paper [1], the possibility of modelling scanner levelling using design densities was investigated. This could be used to test and optimize the intrafield levelling friendliness before any silicon is exposed on the tool. This multi-source data analysis uses scanner log files, GDS's, on-product and bare-wafer focus. They are processed together in a multivariate analysis tooling (Partial Least square regression software) in order to generate the model.

Figure 1: Different data sources and their use in the focus correlation study (GDS: Design layout, Short loop focus monitoring: Single Shot Focal test, On-product focus: Focus Uniformity Map "Bossung top best focus") [1]

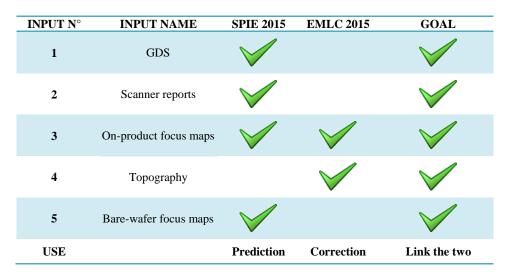

Figure 2: Inputs summary and availability

### II - BEST FOCUS vs. TOPOGRAPHY ANALYSIS

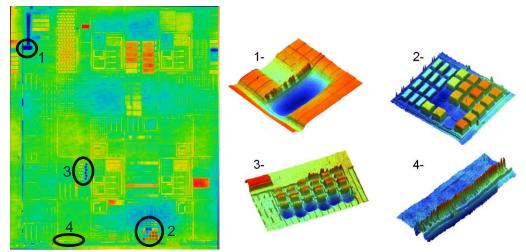

Local topography effect will affect on-product focus on the wafer. In order to correct for these height variations, the scanner performs a levelling optimization. This involves successively measuring the topography on the wafer and then mechanically correcting for it, by moving the stage during the exposure, to keep the wafer within focus. However, this system cannot correct for high frequency topography variations. And the areas where the topography changes are extreme can lead to defocus. In the case of the 14FDSOI development shuttle, several care areas were defined using data extracted from offline topography measurements. Most of these areas are not expected to be present on a product but are necessary for the development of a technology. The topography measurements were done a Veeco WYKO NT9300 tool in LETI

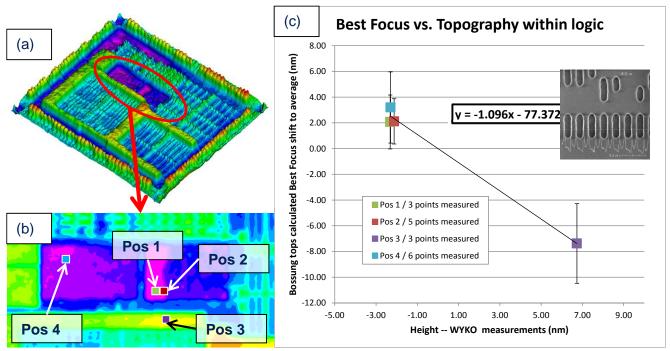

without litho stack [7]. The measurements allow a mapping of one field with pixels of a few  $\mu$ m<sup>2</sup>. Figure 3 shows the mapping obtained for one field as well as some areas were due to high spatial frequency topography locally some high defocus is expected.

Figure 3: Wyko measurements of one field of 14FDSOI chip at Contact layer without Litho stack. Zooming is done on some defocus care areas defined for the 14FDSOI Contact layer

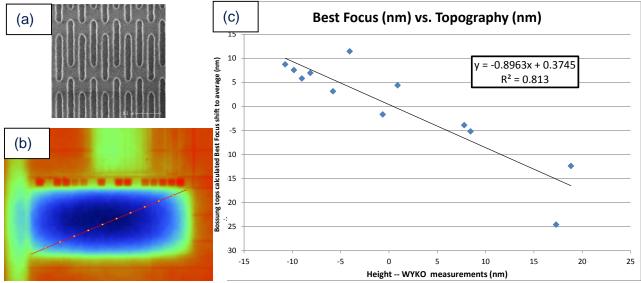

Care area 1 on the shuttle has the worse – but known atypical - local topography. We measured in this area one pattern on a focus matrix wafer for Best Focus determination and analysis. The results of the analysis are given in Figure 4. It shows that the best focus of the pattern and the topography at the same position are correlated linearly with a very high coefficient of correlation:  $R^2 = 0.81$ .

Figure 4: (a) Pattern measured – (b) Position of the measurement points on the area – (c) Best focus vs. topography correlation for care area 1.

The slope of the correlation curve is not 1 but this can be explained by the fact the reference topography measurements were done without any litho stack and that the tri-layer smooths the topography. Mask CD effects were not taken into account here and that may explain the shift of some point from the curve.

In order to test if this can also be seen on the product, some extra measurements were done within the logic, where the topography variations are much smaller. The same structure was measured in two parts of a logic block showing about 9nm height difference. The best focus shift between the different locations was about 11nm.

Figure 5: (a) Logic chip topography mapping - (b) Position of the measurement points on the area - (c) Best focus vs. topography correlation for logic area.

In both cases, a higher topography leads to a negative best focus shift which corresponds to how the focus is referenced in the scanner where a positive focus offset moves the imaging plane (wafer stage) away from the lens.

# **III – PRODUCT LAYOUT AWARE LEVELLING OPTIMIZATION**

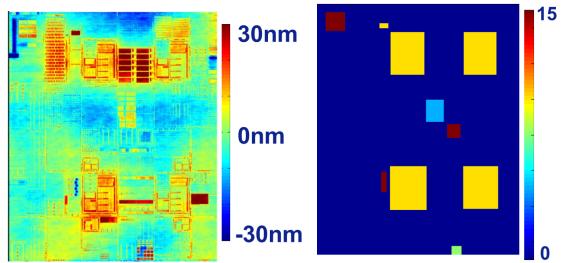

Dense topography information can be used to identify imaging critical locations that are most at risk of causing topography driven focus induced yield loss. Figure 6 shows an example of this process, where weights are specified for different locations in the field.

Figure 6: Intra-field topography measurements (left) and location of selected weight factors for optimization example (right)

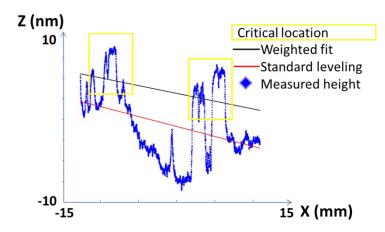

Extra weight is given for the areas that contain most focus critical features. This is done by optimizing the slit z-offset and Ry rotation at each scan position. Figure 7 shows how the slit of the weighted fit is closer to the measured height of the features within the critical locations, with respect to standard levelling.

Figure 7: An example of the weighted fit versus standard levelling slit position at 1 scan location

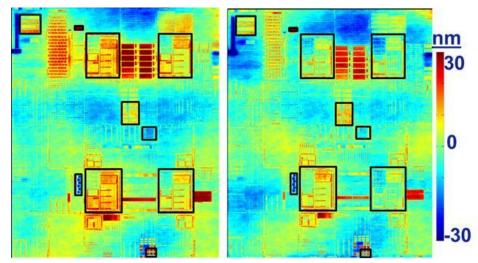

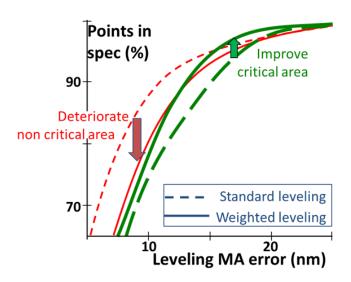

The weighted levelling optimization results in visibly reduced levelling non-correctable moving average errors in the critical locations.

Figure 8: Levelling MA non-correctable error with regular levelling (left) and weighted levelling (right)

This method of optimizing levelling is a trade-off between improving performance in the critical areas and compromising on the performance outside the critical areas. This is visualized in figure 9. Within the critical area the amount of points with a levelling MA error <15nm increases from 90% of points to 95% of points. However, in the non-critical area the amount of points with a levelling MA error <15nm reduces from 95% to 93%. Using the topography information it is possible to visualize the impact applying weight factors before applying them on the scanner.

Figure 9: Levelling MA error points in spec comparison of standard levelling with respect to weighted levelling for critical and non-critical locations

#### CONCLUSION

Topography measurements have been correlated to on-product focus showing that a difference in height can cause focus excursions. Using full field topography measurements, it was possible to determine weight factors for different areas of the field. These weight factors were used to calculate an optimized levelling fit and ultimately correct what matters. This resulted in improved focus performance in critical areas. This method of optimization would be especially useful for development shuttles due to the fact that the process is still being optimized and that some non-critical test chips are present on the reticle.

#### **REFERENCES:**

[1] Simiz, J-G., Hasan, T., Staals, F., Le-Gratiet, B., et al., "Predictability and impact of product layout induced topology on across-field focus control", Proc. of SPIE Vol. 9424, 2015

[2] Seltmann, R., "28nm node process optimization: A Lithographic Centric View", EMLC 30, Proc. of SPIE 9231, 2014

[3] Katakamsetty, U., Colin, H. et al., "Scanner correction capabilities aware CMP / Lithography hotspot analysis", Proc. of SPIE Vol. 9053, 2014

[4] Colin, H., Bin, W. X., et al., "Hotspot Detection and Design Recommendation Using Silicon Calibrated CMP Model", Proc. of SPIE 7275, 2009

[5] Jang, J. H., Park, T. et al., "Focus control budget analysis for critical layers of flash devices", Proc. of SPIE Vol. 9050, 2014

[6] Hunsche, S., Jochemsen, M., et al., "A new paradigm for inline detection and control of patterning defects", Proc. Of SPIE Vol. 9424, 2015

[7] Dettoni, F., et al., "High resolution nanotopography characterization at die scale of 28nm FDSOI CMOS front-end CMP processes", Microelectronic Eng. 113, p105-108, 2014.